With the development of technology in the electronics industry, especially in the transmission interface, from PCI to PCI Express, from ATA to SATA, from the parallel ADC interface to JESD204, from RIO to Serial RIO, and so on, no one has proved the traditional parallel interface. The speed has reached the bottleneck, replaced by a faster serial interface, so the SerDes technology originally used for optical fiber communication has become the mainstream of high-speed serial interfaces. The serial interface is mainly applied with differential signal transmission technology, featuring low power consumption, strong noise immunity, and high speed. The data transmission rate of a serial link interface such as PCI Express® (PCIe®) Gen4 will reach a double-digit gigabit. Transmission rate. As a result, device modeling, interconnect modeling, and analysis methods must evolve to address the ever-decreasing design margins and the more challenging compliance standards that today's engineers face. This series of articles will be in-depth analysis of various aspects, in order to reduce the risk and optimize the design, it is essential to push the analysis to the upstream as far as possible to achieve tradeoffs, feasibility studies, component selection, and constraint acquisition.

Automatic compliance check

With detailed post-layout interconnect and proper execution of the IBIS-AMI model, you can focus on the compliance check for a specific, interesting interface (in this case PCI Express Gen 4).

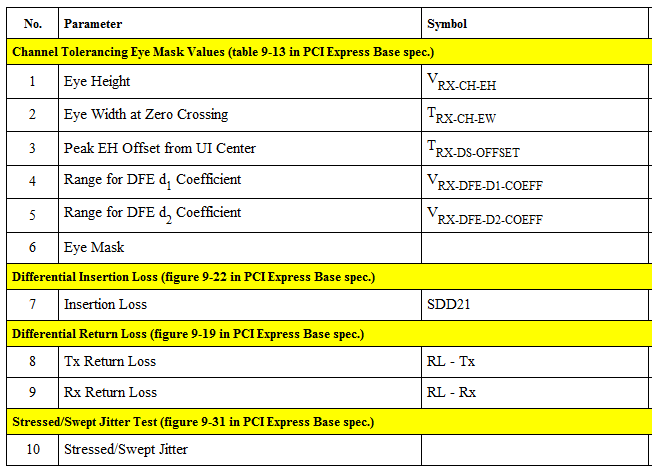

Each interface has its own specific criteria. In this situation, PCI Express identified many eye-related time domain standards, frequency domain standards for passive interconnect channels, and the ability to meet specific jitter tolerance limits.

Evaluating these standards separately can be time consuming, especially if multiple runs are needed to scan the design range and multiple channel models. Automated compliance toolkits for the Universal Serial Link standard often provide simulation tools that can significantly speed up compliance checking and shorten sign-off time.

Figure : PCI Express Compliance Check

Automatically scan critical parameters and flag compliance failures to better cover your serial link design and help examine other areas of your concern.

Figure: PCI Express Compliance Check Results

Another major benefit of using the Compliance Toolkit is the ability to use related templates during the pre-layout phase. As discussed earlier, establishing an early test platform for a viable trade-off is crucial. However, at this stage there is usually a lack of real models of the necessary modules. Sometimes it is necessary to use the "placeholder" model. The templates provided with the Auto Compliance Kit are usually pre-filled with the actual topology and model, including the specification-level model of the SerDes IBIS-AMI model of the transmitter and receiver, and constructed according to the reference parameters described in the specifications of that particular standard. These templates and their associated models provide a good starting point for your pre-layout test bed development, helping to minimize the time required to start and run and avoid design rework.

to sum up

This article summarizes the eight articles in this series on "The SI Method for Multi-Gigabit Serial Link Interfaces." The previous blog post topics in this series were:

Push SI upwards by "top-down" approach

Pre-layout modeling of PCB interconnections

IBIS-AMI modeling

Enable constraint-driven design

Efficient interconnection extraction

Simulation using IBIS-AMI model

Reverse channel training

The two-digit gigabit data rate serial link interface has its unique design challenges. Starting from the pre-design phase, top-down analysis methods can mitigate the associated risks and avoid costly, time-consuming redesigns. The result of this work is to determine the wiring rules required to constrain the physical layout. Particular attention is paid to via structures to control insertion loss and return loss; the method of introducing well-known via structures into the layout is critical. The IBIS-AMI model is needed to represent the adaptive equalization and reverse channel capabilities seen at these data rates, and the specifications can be rapidly built upon demand. The "Cut & stitch" technique can be applied after interconnection extraction is required to extract the wiring, while achieving full-wave simulation accuracy while avoiding the computational loss of end-to-end full-wave 3D extraction. The Automated Compliance Toolkit facilitates the successful signing of serial link designs while providing a valuable starting point for the pre-layout analysis phase.

Ningbo Autrends International Trade Co.,Ltd. , https://www.ecigarettevapepods.com