Although the number of such channels has been widely accepted by the market for a long time, is this still suitable for today's embedded systems? This is a question worth considering for oscilloscope manufacturers and embedded system designers. The manufacturer must know whether it provides the test functionality that the customer actually needs and is willing to pay for. Designers need tools that are suitable for the job.

Thinking about this issue has driven the implementation of multiple research projects, and embedded system engineers from around the world are investigating the number of oscilloscope channels in greater depth. The latest 5 series of MSOs reflect the results of these studies in many places, increasing the number of analog channels provided to 6 or 8 and providing 8 to 64 digital channels. It is also possible to reconfigure the digital channel during operation.

Given that the four-channel MSO has achieved impressive results in the past few years, it can be said that the traditional number of analog channels and digital channels can fully meet the needs of most embedded designers. More specifically, designers strive to make 4 The channel is sufficient. But a large percentage of engineers (35% of our research) claim that the number of ideal analog channels they need is eight.

In the past, when these engineers needed more than four analog inputs, they tried to use two oscilloscopes simultaneously. This practice of "cascading" multiple oscilloscopes presents multiple challenges. For simultaneous acquisition, multiple oscilloscopes must be triggered at the same point in time, both for cable (or dual probe) requirements and for creative trigger settings. It's also hard to compare the data on the two displays, so many engineers get the data from two oscilloscopes and then use the computer to close the waveforms for evaluation. Even if the two oscilloscope models are identical, this synchronization can take a long time, and if you are using a different oscilloscope model, the problem will be more.

In terms of digital channels, it has been proven that the reduction in numbers is as important as the increase in numbers. In some cases, many engineers have a lot of frustration because they are forced to buy 16 digital channels, but in reality only need 8 digital channels. In our study, about 75% of respondents claimed that they did not want 16 digital channels, some wanted more, and some wanted less.

For embedded system designers, flexibility is more important than the number of channels in many of the oscilloscope's features. Our research found that 79% of embedded engineers want oscilloscopes to be "for future needs" and have multiple functions to meet the needs of design teams facing tremendous pressure.

The most common answer is when we talk to embedded designers about which stages require more channels and greater flexibility during system level debugging. When multiple subsystems begin to merge together, multiple processors, multiple power supplies, multiple serial buses, and multiple I/O devices, system-level viewing capabilities become critical. In the traditional debugging mode of the oscilloscope, engineers need to use 2 channels or 4 channels to capture data multiple times, and trace back the signal path to find the root cause of the problem. Many systems today handle input from multiple sensors, drive multiple actuators, and communicate over multiple buses. Traditional debugging methods can encounter many problems. These embedded computing systems include sensors, accelerators, processing power, and communications to form distributed smart devices in the growing Internet of Things (IoT).

Our research found that another pain point for embedded engineers stems from the proliferation of power supplies in today's systems. To optimize power consumption, performance, and speed, even a relatively simple system might have a 12 V total power supply, multiple 5 V supplies, a 3.3 V supply, and a 1.8 V supply. Verifying and commissioning the power-on and power-off sequences of these power supplies, especially with respect to other control signals or status signals on the board, requires more channels and more testing.

Some creative engineers report that they use a variable threshold on the digital MSO channel to verify the power sequence. In this case, they set the threshold of the digital channel to be slightly lower than the nominal voltage of the power supply, and use this setting to generate a "timing diagram" of the power supply, reset line, interrupt, status line, and so on. This method has a significant drawback, that is, the power supply is represented by a binary waveform, ignoring the analog characteristics of the signal. Most engineers prefer to use analog channels to perform this type of testing and debugging.

For many applications, a traditional configuration of four analog channels/16 digital channels may be sufficient. But if you encounter new problems, and we will definitely encounter new problems, then it is best to know that there are finally some other options to choose from.

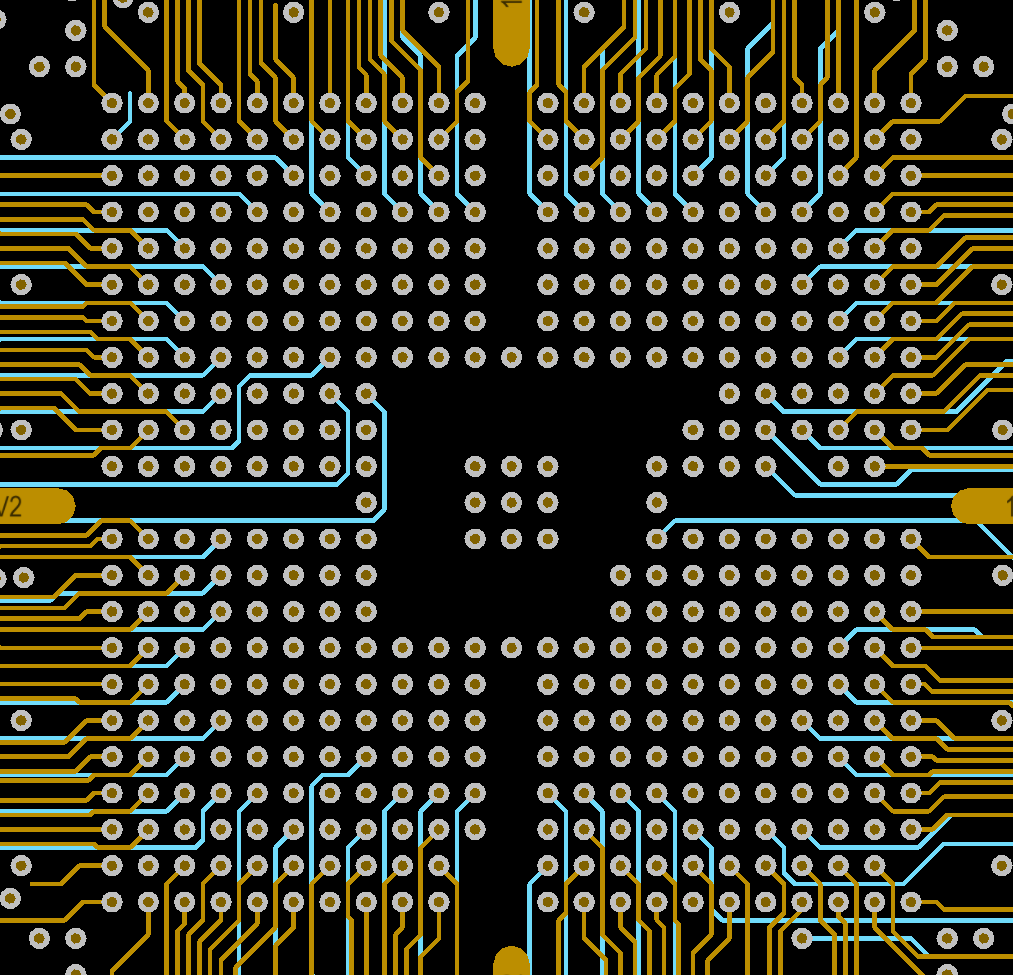

Ball Grid Array (BGA), a type of surface-mount packaging (a chip carrier) used for integrated circuits.

OEM needs smaller and more diverse packaging options to meet product design challenges and maintain cost competitiveness in their respective markets. Ball grid array (BGA) packaging is becoming more and more popular to meet these design requirements. In addition, they are ideal solutions, because I/O connections are located inside the device, increasing the ratio of pins to PCB area. In addition, BGA with strong solder balls is stronger than QFP lead, so it is more robust.

Ball-Grid Array (BGA) Packages Become PCB Design Mainstream

BGA PCB Design Guidelines And Rules

BGA PCB Design Rules

In order to keep up with the technological progress of chip manufacturers, BGA software packages for embedded design have made remarkable progress in the past few years.

This special type of packaging can be decomposed into standard BGA and micro BGA.

With today's electronics technology, the demand for I/O availability poses a number of challenges, even for experienced PCB designers, due to multiple exit routes.

Correct BGA partitioning first takes into account uniformity of the partitioning, itself. Because, precise BGA partitioning on a PCB is a crucial design aspect to minimize or eliminate crosstalk and noise, as well as manufacturing issues.

Memory signals need special consideration during BGA partitioning. They need to be away from oscillating signals and power supply switching. This is important because memory signals needs to be clean. If traces carrying these signals are in the proximity of oscillating signals or switching power supply signals, they produce ripples in the memory signal traces, thereby reducing system speed. The system is operational, but at less than optimal speed levels.

BGA PCB Design Guidelines

BGA Design Strategy 1: Define an appropriate exit path

The main challenge for PCB designers is to develop appropriate exit routes without causing manufacturing failures or other problems. Several PCBs need to ensure proper fan-out wiring strategies, including pad and pass size, I/O pin number, layers required for fan-out BGA and line width spacing.

BGA Design Strategy 2: Identify the Layers Required

Another question is how many layers the PCB layout should have, which is by no means a simple decision. More layers mean higher overall cost of the product. On the other hand, sometimes you need more layers to suppress the amount of noise PCB may encounter.

Once the alignment and space width of PCB design, the size of through holes and the alignment in a single channel are determined, they can determine the number of layers they need. Best practice is to minimize the use of I/O pins to reduce the number of layers. Usually, the first two outer sides of the device do not need through holes, while the inner part needs to arrange through holes below them.

Many designers call it dog bones. It is a short path of the BGA device pad, with a through-hole at the other end. The dog bone fan comes out and divides the equipment into four parts. This allows the remaining internal padding to be accessed by another layer and provides escape paths away from the edge of the device. This process will continue until all mats are fully developed.

BGA Package Types

There are six different BGA packages.

1. Moulded Array Process Ball Grid Array (MAPBGA): It is a BGA package which provides low inductance and simple surface mounting.

2. Plastic Ball Grid Array (PBGA): Again, this BGA package provides low inductance, simple surface mounting, high reliability and is cheap.

3. Thermally Enhanced Plastic Ball Grid Array (TEPBGA): Just like its name sound, this BGA package can handle great levels of heat dissipation. Its substrate has solid copper planes.

4. Tape Ball Grid Array (TBGA): You can use this BGA package as a solution for medium- to high- end applications.

5. Package on Package (PoP): It will permit you to put a memory device on some base device.

6. Micro BGA: This BGA package is quite small when compared with standard BGA packages. Currently, you will see 0.65, 0.75 and 0.8 mm pitch size dominating in the industry.

BGA PCB Assembly

Previously, Engineers were not sure whether PCB BGA assembly would be able to achieve the reliability level of traditional SMT methods. However, at present, this is no longer a problem, because BGA has been widely used in prototype PCB assembly and mass production PCB assembly.

You will need to use reflow methods to solder a BGA package. Because only reflux method can ensure solder melting under BGA module.

We have a wealth of experience handling all types of BGAs, including DSBGA and other Complex Components, from micro BGAs (2mmX3mm) to large size BGAs (45 mm); from ceramic BGAs to plastic BGAs. We are capable of placing minimum 0.4 mm pitch BGAs on your PCB.

PCB BGA Advantages

With PCB BGA, you will get the following advantages:

1. BGA package eliminates the issue of developing small packages for ICs with lots of pins.

2. Again, when compared with packages with legs, The BGA package has a lower thermal resistance when placed on the PCB.

3. Do you know which property causes unwanted signals distortion in high-speed electronic circuits? The unwanted inductance in an electrical conductor is responsible for this phenomenon. However, BGAs have very little distance between PCB and the package which in turn leads to lower lead inductance. Thus, you will get top-class electrical performance with pinned devices.

4. With BGAs, you can effectively utilize your printed circuit board space.

5. Another advantage that will come with BGA is the reduced thickness of the package.

6. Last but not least, you will get enhanced re-workability because of bigger pad sizes.

Additional Information

Via in PAD(VIP) PCB

6 Layer BGA PCB

Bare PCB,BGA PCB,BGA Circuit Board,BGA PCB Design

JingHongYi PCB (HK) Co., Limited , https://www.pcbjhy.com